1. Convert project to JavaEE project.

ref: http://www.mkyong.com/java/how-to-convert-java-project-to-web-project-in-eclipse/

Here is the steps to convert Java Project to Web Project in Eclipse

ref: http://www.mkyong.com/java/how-to-convert-java-project-to-web-project-in-eclipse/

Here is the steps to convert Java Project to Web Project in Eclipse

1) Create a empty dynamic web project and click on the .project file

2) Copy “web project” facet buildCommand and paste within “java project” .project buildSpec tag

3) Copy “web project” facet nature and paste within “java project” .project natures tag

P.S Be careful of the

.project xml tag, make sure you paste into a correct location.

4) Save it.

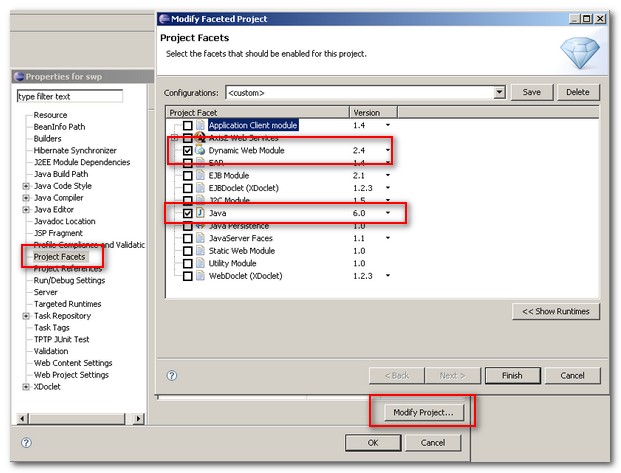

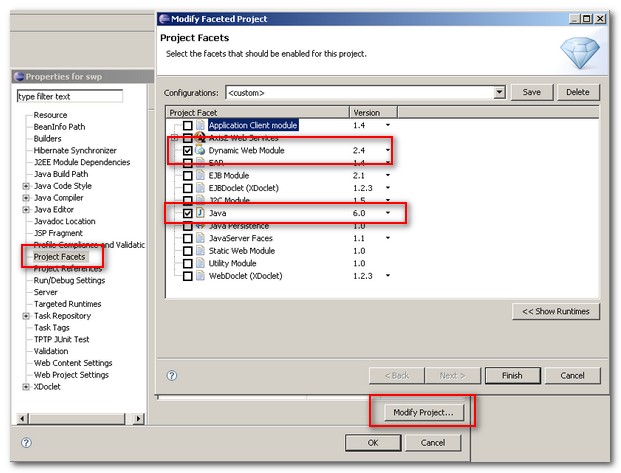

5) Right click on Java Project, click properties.

6) Select Project Facets and click modify project button.

7) Click Dynamic Web Module and Java check box.

Finished, Now your java project has been converted into a web project.

2. Config the WebContent folder

Update

org.eclipse.wst.common.component file in .settings directory and wb-resource elements:3. Add User lib's *.jar files into *war

The jar dependencies for Eclipse to include in a war file not placed in WEB-INF/lib is not managed by the usual "project export/imports" but by a separate panel (3.6: Deployment Assembly, 3.5: Java EE Module Dependencies) in the preferences of the dynamic web project.